ISSIE (Interactive Schematic Simulator and Integrated Editor) represents a significant contribution to educational software for digital electronics and computer architecture. As part of the High-Level Programming module at Imperial College London, this project involved substantial improvements to an open-source application actively used in teaching thousands of students at one of the world’s leading engineering institutions.

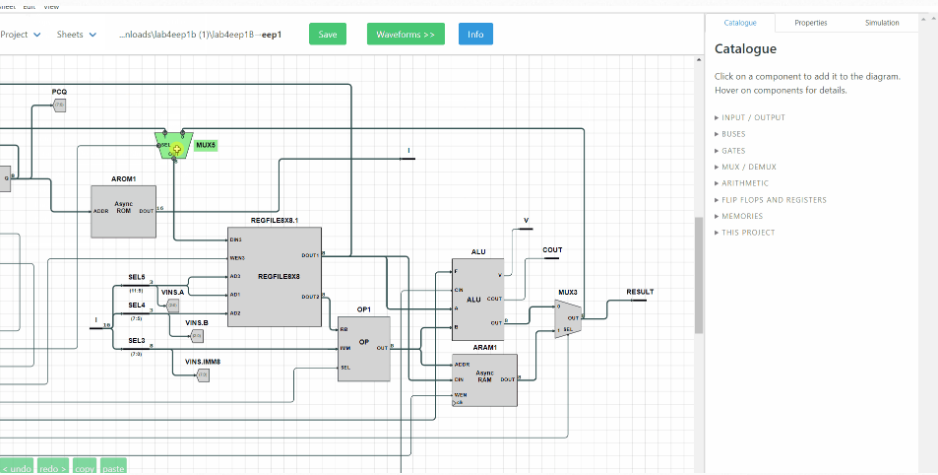

The application enables students and hobbyists to design digital circuit schematics through an intuitive drag-and-drop interface and simulate their behavior in real-time. ISSIE stands out for its beginner-friendly approach, providing clear error messages and visual clues that guide users toward correct implementations rather than leaving them confused when things go wrong. This pedagogical focus makes it an invaluable tool for learning digital electronics concepts.

The project involved working as part of a collaborative development team to overhaul the DrawBlock component, which handles the core rendering and interactive functionality of the schematic editor. Previous implementations relied on the JavaScript Draw2D library, which suffered from performance degradation with complex circuits and exhibited various bugs that hindered the user experience.

The team undertook a complete reimplementation of the drawing subsystem in pure F#, leveraging the Elmish Model-View-Update framework for reactive user interface development. This functional approach provides significant advantages in maintainability and correctness compared to traditional imperative GUI programming. The MVU pattern ensures predictable state management, making it easier to reason about application behavior and implement new features reliably.

Key contributions included implementing component rotation capabilities, allowing users to orient circuit elements in any direction for cleaner schematic layouts. Enhanced wire routing functionality enables connections in arbitrary orientations, providing much greater flexibility in circuit design. Improvements to custom component port management allow users to reposition connection points, accommodating diverse design patterns and reducing visual clutter.

The technical implementation demonstrates mastery of functional programming principles applied to practical software engineering. The use of F# throughout the codebase enables the Fable compiler to transpile functional code into optimized JavaScript, running seamlessly in an Electron desktop application framework. This technology stack provides true cross-platform support across Windows, macOS, and Linux while maintaining a unified codebase.

ISSIE’s architecture implements nearly 50,000 lines of F# code, equivalent to approximately 150,000 lines in typical object-oriented languages due to the conciseness of functional programming. The implementation follows almost pure functional programming principles without assignment, using immutable data structures and pure functions throughout. This approach significantly enhances code maintainability and reduces the surface area for bugs.

The digital simulator component uses an innovative approach combining functional programming robustness with high performance through write-once semantics on mutable JavaScript typed arrays. This hybrid strategy achieves the correctness guarantees of pure functional code while maintaining the speed necessary for simulating large circuits in real-time.

ISSIE provides an extensive component library including low-level gates and flip-flops as well as higher-level blocks such as RAMs, ROMs, n-bit registers, and adders. Special components like Bus Select and Bus Compare enable complex combinational logic without writing HDL code. The hierarchical design system allows users to create custom components from existing designs and reuse them across projects, teaching proper abstraction and modularity principles.

Integration capabilities include Verilog output generation, enabling ISSIE designs to be synthesized on FPGAs or imported into more advanced design tools. This bridges the gap between educational simulation and real hardware implementation, allowing students to see their designs running on physical devices. The ISSIE-Stick hardware integration provides a streamlined path from schematic to FPGA deployment.

The waveform simulator enables detailed timing analysis, showing how signals propagate through circuits. Viewer components can be placed throughout hierarchical designs to observe internal node behavior during simulation, essential for debugging complex systems. Memory components support direct editing and import/export functionality, facilitating testing with realistic data patterns.

Project management features organize design files within project directories, with automatic backup systems preserving design history for recovery if needed. The intuitive interface guides users through project creation, component placement, wiring, and simulation with minimal learning curve.

This contribution to ISSIE demonstrates ability to work on large, established codebases with sophisticated architectures, collaborate effectively within development teams, apply functional programming principles to real-world software engineering challenges, and create software that directly impacts education for future engineering generations. The project represents not just technical achievement but meaningful contribution to the educational infrastructure of a world-renowned institution.